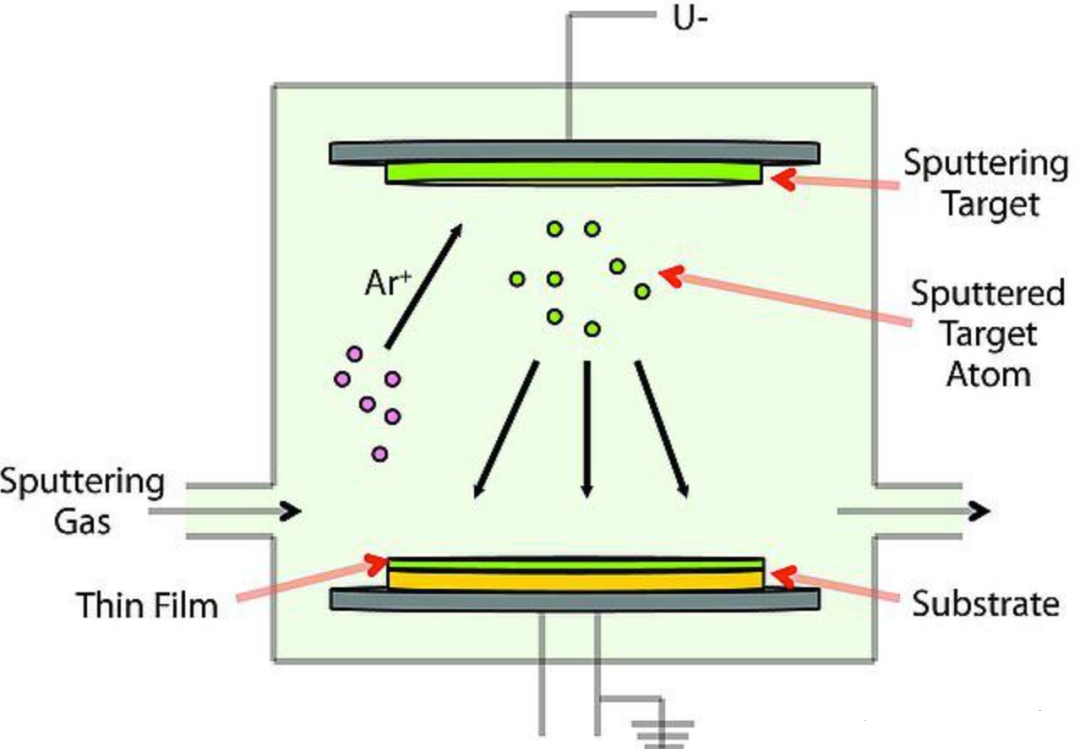

Integrated circuits are built layer by layer on silicon wafers using precisely engineered materials: photoresists for patterning, metal interconnect materials for wiring, insulating materials for isolation, and high-purity metal targets for thin-film formation. In Physical Vapor Deposition (PVD), magnetron sputtering ejects atoms from these targets—such as Ti, Ta, Cu, Al—onto wafers to create adhesion layers, barrier liners, seed layers, contacts, and caps with nanometer control. Modern lines demand film thickness accuracy of ±1–2% and within-wafer uniformity ≤2–3% (1σ) across 200–300 mm wafers to meet timing, leakage, and reliability specs.

High-purity metal targets minimize contaminants (O, C, N, metallic tramp), cutting defectivity by 20–50% in sensitive nodes and stabilizing resistivity and stress. Titanium and tantalum targets enable diffusion barriers and adhesion to dielectrics; copper targets form low-resistance interconnects; aluminum targets remain essential in analog, power, and RF modules. Sputtering integrates seamlessly with lithography-defined photoresists and dielectric stacks, allowing conformal coverage for vias and trenches, and reliable interfaces for multi-level metals. As device geometries approach single-digit nanometers, target purity, microstructure, and bonding to backplates become as critical as tool design, ensuring repeatable PVD deposition, tighter process windows, and scalable yield from R&D to high-volume manufacturing.

1. Application requirements for sputtering targets

1.1 Purity: the cornerstone of stable plasmas and clean films

The purity of a metal sputtering target dictates plasma stability and thin-film cleanliness. Excess impurities perturb glow discharge, induce micro-arcing, and seed particles that degrade film continuity and cause local thickness or composition excursions. These defects can lead to leakage, shorts, or opens in dense interconnects and vias. Hence high purity—often ultra-high purity—is foundational.

· Purity benchmarks:

· Precious-metal IC targets typically require 5N (99.999%) to 6N (99.9999%).

· Semiconductor-grade metal targets specify quantified limits for at least ~40 impurity elements, including:

· Alkali metals (K, Na, Li)

· Radioactive elements (U, Th)

· Transition metals (Fe, Ni, Cr, Cu)

· Halogens (Cl)

· Light elements/gases (C, O, N, H)

· Rationale:

o Alkalis can be mobile and cause leakage.

o Transition metal tramp elements raise resistivity, shift work function, or catalyze corrosion.

o O/N/H/C increase arcing risk and alter film stoichiometry, particularly in reactive sputtering (e.g., TiN).

1.2 Grain size and crystallographic texture

Grain size directly affects sputter yield and erosion behavior. Atoms at grain boundaries are less tightly bound than those within grains; therefore, fine-grained targets (more boundaries) sputter more uniformly and can exhibit higher effective rates in the erosion racetrack.

· Typical requirement:

o IC metal targets often specify average grain sizes below 100 μm, with narrow distributions.

· Benefits of fine and uniform grains:

o Smoother erosion track, reduced rate drift across target life.

o Better within-wafer thickness uniformity and improved repeatability across lots.

o Lower likelihood of localized hot spots that trigger arcs or particles.

Texture control (minimizing strong, unfavorable crystallographic orientations) further stabilizes sputter yield and secondary electron emission, helping maintain uniformity at 200–300 mm scales.

1.3 Density and residual porosity

Low-density targets contain pores that trap gases and impurities. During sputtering, trapped species outgas, destabilize plasma, and cause abnormal discharges, ultimately degrading film properties.

· Best practice:

o Achieve relative density ≥99.5% of theoretical via hot isostatic pressing (HIP) or optimized forging/rolling schedules.

o Validate with ultrasonic testing and microstructural mapping to identify porosity or inclusions.

1.4 Surface quality and macroscopic geometry

Surface protrusions and sharp edges act as field concentrators, promoting local dielectric breakdown (tip effect) and arcing.

· Geometric/finish controls:

o Tight flatness and straightness tolerances across the target face.

o Controlled roughness (Ra) suited to the tool’s ignition and conditioning sequences.

o Clean chamfers and sealed edges to reduce flaking.

o Backing/bond-line planarity to ensure even thermal transfer.

2. Applications of different metal sputtering targets in ICs

Different target materials deliver distinct electrical, chemical, and mechanical properties. Their selection is tied to the device node, module (FEOL/MOL/BEOL), and integration stack.

2.1 Copper, aluminum, and their alloys

· Aluminum (Al) and Al alloys:

o Historically the dominant interconnect metal above ~90–110 nm nodes due to cost and process maturity.

o Alloys such as Al-Cu or Al-Si improve electromigration resistance and reduce hillock formation.

o Used in logic, analog, power, and RF where legacy flows and high-voltage reliability are critical.

· Copper (Cu) and Cu alloys:

o Became standard below ~90–110 nm for lower resistivity and better electromigration performance.

o Alloying with Mn, Al, or other elements can form self-forming barriers, reduce diffusion, and tune grain growth to lower line resistance.

· Integration notes:

o Copper requires barrier/liner stacks (e.g., Ta/TaN, sometimes TiN in specific roles) to prevent Cu diffusion into dielectrics and silicon.

o Seed layers are typically sputtered before electroplating to ensure continuity in high-aspect trenches and vias.

2.2 Titanium and titanium alloy targets

Titanium (Ti) combines strong adhesion with Corrosion resistance, making it versatile for multiple roles:

· Barrier and adhesion layers for Al interconnects at ~130–180 nm nodes on 8-inch silicon wafers.

· Reactive sputtering to form high-density TiN for barriers, hard masks, and capping layers.

· Bottom liner and adhesion layer beneath CVD W plugs.

· Ti-silicide related contact schemes and anti-reflective coatings to stabilize lithographic Optical response.

Ti and TiN suppress high-temperature diffusion (e.g., Al spiking), protecting junction integrity and improving device reliability. Their wetting characteristics enhance film continuity on dielectrics and silicon.

2.3 Tantalum and tantalum alloy targets

Tantalum (Ta) is a refractory metal with a very high melting point, high density, excellent ductility, and strong chemical stability:

· Primary diffusion barrier and liner for Cu interconnects below ~90 nm.

· Ta/TaN stacks inhibit Cu diffusion into low k dielectrics and silicon while maintaining adhesion.

· Ta-based targets also enable high k gate dielectric oxide stacks in certain flows, supporting further transistor scaling and drive-current improvements.

2.4 Cobalt and nickel–platinum targets

Cobalt (Co) and nickel–platinum (Ni–Pt) are essential for contact engineering via silicide formation:

· Co silicide (CoSi2): commonly used around 130–90 nm logic processes for source/drain and gate contacts.

· Ni–Pt silicide (NiPtSi): increasingly adopted from ~65–20 nm logic nodes for lower contact resistance and improved thermal stability; also applicable in 1X nm memory where requirements are comparatively relaxed.

· Integration highlights:

o Films are first sputtered, then reacted to form the desired silicide with tuned phase and sheet resistance.

o Composition precision and impurity control are critical to avoid spurious phases and junction leakage.

3. How sputtering targets are engineered and produced

Modern targets are engineered to deliver High purity, precise grain size control, high density, and robust thermal management.

· Purification routes:

o Chemical refining (electrorefining, solvent extraction) to remove specific impurities.

o Physical refining (electron-beam melting, vacuum arc remelting, zone refining, vacuum distillation) to reach “the last nine” in purity.

o Analytical controls: GDMS/ICP-MS for metallic impurities; LECO for O/N/H; TOC for carbon; radioactivity screens for U/Th.

· Microstructure control:

o Forging/rolling schedules followed by stress-relief anneals to achieve fine, equiaxed grains and reduce texture.

o HIP densification to close residual porosity and improve mechanical integrity.

· Backing and bonding:

o Diffusion-bonding to high-thermal-conductivity backplates (commonly Cu) for stable heat extraction.

o Bond-line NDT to prevent hot spots that cause arcing or composition drift.

· Surface finishing:

o Precision machining in inert or dry-room conditions to minimize oxygen pickup.

o Edge conditioning, flatness control, and protective packaging to preserve surface quality.

4. Why these target attributes matter for device performance

· Uniform films at nanometer scale:

o Fine-grained, dense, and smooth targets produce stable erosion tracks, improving within-wafer thickness uniformity and wafer-to-wafer repeatability—often within ≤2–3% (1σ) on 200–300 mm wafers.

· Electrical properties and reliability:

o Clean, controlled composition minimizes resistivity variability, reduces via/contact resistance, and suppresses electromigration and stress migration.

· Interface integrity:

o Proper adhesion and barrier layers prevent interdiffusion and chemical attack during downstream cleans and anneals, preserving device parameters and yield.

· Lithography synergy:

o Anti-reflective and capping layers tuned via sputtering stabilize optical constants, improving photoresist pattern fidelity and line-edge roughness.

5. Process integration across nodes and modules

Sputtering targets engage with every major module of IC fabrication:

· FEOL/MOL:

o Contact metallization and silicide formation using Co and Ni–Pt systems.

o Metal gate stacks that may include Ti/TiN insertions for work-function and thermal stability.

· BEOL:

o Al and Cu interconnects with barrier/liner stacks (Ti/TiN for Al flows; Ta/TaN for Cu flows; TiN as hard mask or cap).

o W plugs with Ti/TiN liners for reliable fill and low-resistance contacts.

· Advanced packaging:

o Under-bump metallization (UBM), redistribution layers (RDL), and caps where Ti/TiN’s adhesion, wetting, and Corrosion resistance are valuable.

At sub-7 nm nodes, shrinking geometries and fragile low k dielectrics tighten process windows further:

· Targets with even finer, more uniform grains reduce racetrack roughness and particle generation during end-of-life.

· Purity escalates to reduce outgassing and arcing; strict control of alkalis/halogens and O/N/H/C becomes mandatory.

· Thermal management and bonding quality stabilize the erosion groove and sustain deposition rate and stoichiometry, especially in reactive TiN processes.

6. Best practices for stable sputtering in IC production

· Control temperature, time, and atmosphere throughout manufacturing and use:

o Inert handling during machining and assembly.

o Pre-sputter conditioning to degas surfaces and stabilize the plasma.

· Reactive sputtering controls for nitrides:

o Closed-loop nitrogen partial-pressure control or optical emission feedback to avoid hysteresis.

o Fast arc-detection and quench electronics to protect wafers and maintain yield.

· Metrology and SPC:

o Real-time rate and uniformity monitoring, with ex-situ verification (XRR, four-point probe, XRD, SIMS).

o Particle scans to anticipate end-of-life and plan target changeovers without risking high-value wafers.

Outlook

As integrated circuits continue to scale and diversify into diverse product categories (including logic circuits, SRAM/DRAM, 3D NAND, RF, image sensors, and more), the demand for sputtering targets is growing. High-purity metal targets with fine microstructures, high density, and pristine surfaces have become strategic assets. Shaanxi Shenglian Yijing Technology Co., Ltd. is a supplier of highly consistent, low-defect targets. Contact us to achieve tighter process windows, higher yields, and a smoother transition to new materials and device architectures.

Frequently Asked Questions and Answers

Q1: How are sputtering targets used in the metalization layer deposition of integrated circuits, and what specific roles do they play in forming conductive paths between transistors?

A1: Targets provide the source atoms for thin films that build interconnect stacks. Al or Cu targets form the metal wiring, while Ti/TiN or Ta/TaN targets provide adhesion and diffusion barriers that keep metals from invading dielectrics or silicon. Additional targets supply seed and cap layers to ensure continuity and reliability. Together, these films connect transistor source/drain/gate terminals into functional circuits with low resistance and high electromigration margins.

Q2: How are different material types of sputtering targets (e.g., titanium, copper, aluminum) used in integrated circuits, and how do their properties influence the choice for specific IC components like interconnects or barriers?

A2: Copper targets are chosen for low-resistance interconnects below ~90–110 nm, while aluminum targets remain common above those nodes and in analog/power applications. Titanium targets are favored for adhesion layers and as precursors to TiN barriers/hard masks; tantalum targets are preferred barriers/liners for Cu due to superior diffusion blocking. Cobalt and nickel–platinum targets enable low-resistance silicide contacts. Each material’s conductivity, diffusion behavior, adhesion, and thermal stability drives its placement in the stack.

Q3: How are sputtering targets used in the fabrication of advanced integrated circuits with sub-7 nm nodes, and what adjustments in target design or deposition processes are required to meet miniaturization demands?

A3: Sub-7 nm flows require ultra-clean, fine-grained, high-density targets to minimize particles and stabilize erosion. Purity specifications tighten (especially for O/N/H/C and alkalis), and bond-line thermal performance becomes critical to prevent hot spots and arcing. Processes adopt closed-loop reactive control for TiN, improved magnet packs for uniformity, HiPIMS or collimated PVD for better step coverage, and rigorous SPC to maintain ≤2–3% (1σ) thickness uniformity across 300 mm wafers. These adjustments collectively preserve conductivity, barrier integrity, and yield at extreme scales.